- (a) an 8:1 multiplexer

- (b) a 4:1 multiplexer and one inverter

- (c) a 2:1 multiplexer and two other logic gates

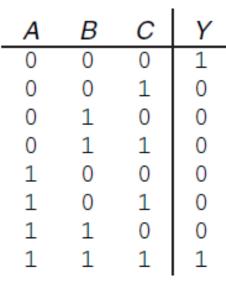

| Α | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

- (a) an 8:1 multiplexer

- (b) a 4:1 multiplexer and one inverter

- (c) a 2:1 multiplexer and two other logic gates

|   |   |   |   | ABC   |

|---|---|---|---|-------|

| А | В | С | Y |       |

| 0 | 0 | 0 | 1 | 000   |

| 0 | 0 | 1 | 0 | 001   |

| 0 | 1 | 0 | 0 | 010   |

| 0 | 1 | 1 | 0 | 011   |

| 1 | 0 | 0 | 0 | 100 7 |

| 1 | 0 | 1 | 0 | 101   |

| 1 | 1 | 0 | 0 | 110   |

| 1 | 1 | 1 | 1 | 111   |

|   |   |   |   |       |

| Α | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

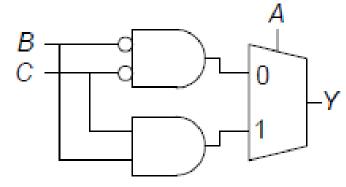

- (a) an 8:1 multiplexer

- (b) a 4:1 multiplexer and one inverter

- (c) a 2:1 multiplexer and two other logic gates

| Α | В | Υ |

|---|---|---|

| 0 | 0 | C |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | С |

|               | AB              |            |

|---------------|-----------------|------------|

| o N-          |                 |            |

|               | 00              |            |

|               | <del> </del> 01 | V          |

|               | 10              | - <i>T</i> |

|               | لــ 11 ا        |            |

| $\rightarrow$ | , [             |            |

- (a) an 8:1 multiplexer

- (b) a 4:1 multiplexer and one inverter

- (c) a 2:1 multiplexer and two other logic gates

| Α | Υ               |

|---|-----------------|

| 0 | $\overline{BC}$ |

| 1 | BC              |

|   |                 |

| Α | В | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

|   |   |   | ' |

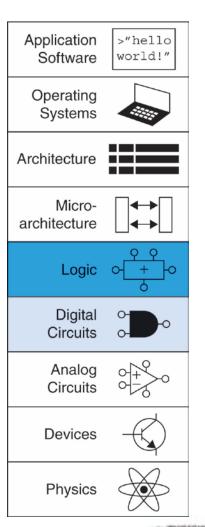

#### Chapter 3

#### Digital Design and Computer Architecture, 2<sup>nd</sup> Edition

David Money Harris and Sarah L. Harris

#### Chapter 3 :: Topics

- Introduction

- Latches and Flip-Flops

- Synchronous Logic Design

- Finite State Machines

- Timing of Sequential Logic

- Parallelism

#### Introduction

- Outputs of sequential logic depend on current and prior input values – it has memory.

- Some definitions:

- State: all the information about a circuit necessary to explain its future behavior

- Latches and flip-flops: state elements that store one bit of state

- Synchronous sequential circuits: combinational logic followed by a bank of flip-flops

## Sequential Circuits

- Give sequence to events

- Have memory (short-term)

- Use feedback from output to input to store information

#### State Elements

- The state of a circuit influences its future behavior

- State elements store state

- Bistable circuit

- SR Latch

- D Latch

- D Flip-flop

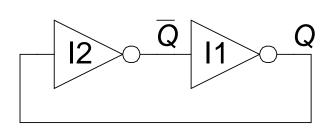

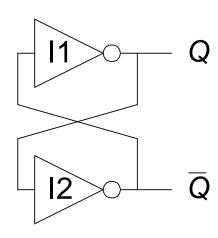

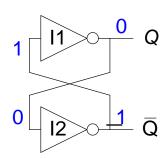

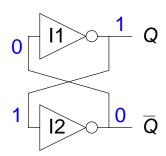

#### **Bistable Circuit**

- Fundamental building block of other state elements

- Two outputs: Q,  $\overline{Q}$

- No inputs

## Bistable Circuit Analysis

Consider the two possible cases:

$$-Q = 0$$

:

then  $\overline{Q} = 1$ ,  $Q = 0$  (consistent)

$$-Q = 1$$

:

then  $\overline{Q} = 0$ ,  $Q = 1$  (consistent)

- Stores 1 bit of state in the state variable, Q (or  $\overline{Q}$ )

- But there are no inputs to control the state

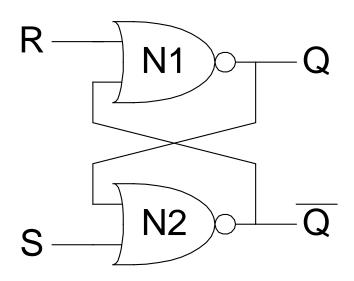

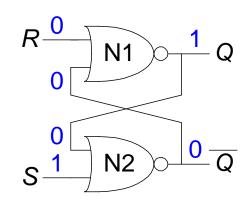

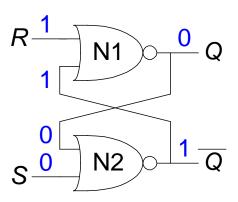

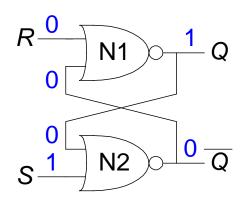

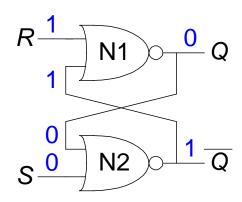

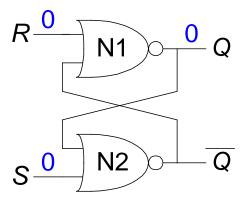

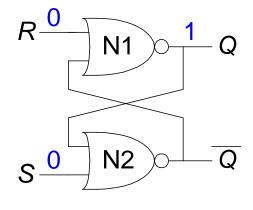

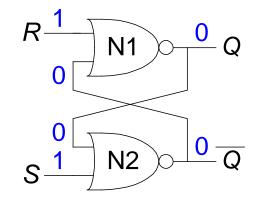

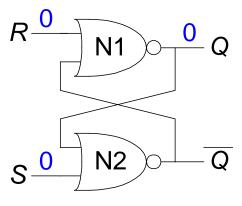

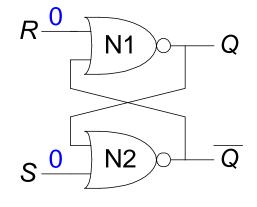

# SR (Set/Reset) Latch

SR Latch

• Consider the four possible cases:

$$-S=1, R=0$$

$$-S=0, R=1$$

$$-S=0, R=0$$

$$-S=1, R=1$$

$$-S=1, R=0$$

:

then  $Q=1$  and  $\overline{Q}=0$

$$-S=0, R=1$$

:

then  $Q=1$  and  $\overline{Q}=0$

$$-S=1, R=0$$

:

then  $Q=1$  and  $\overline{Q}=0$

Set the output

$$-S=0, R=1$$

:

then  $Q=1$  and  $\overline{Q}=0$

Reset the output

$$-S=0, R=0$$

:

then  $Q=Q_{prev}$

$$Q_{prev} = 0$$

$$Q_{prev} = 1$$

$$-S = 1, R = 1$$

:

then  $Q = 0, \bar{Q} = 0$

$$-S=0, R=0$$

:

then  $Q=Q_{prev}$

**Memory!**

$$Q_{prev} = 0$$

$$Q_{prev} = 1$$

$$-S=1, R=1$$

:

then  $Q=0, \bar{Q}=0$

Invalid State

$\bar{O} \neq \text{NOT } O$

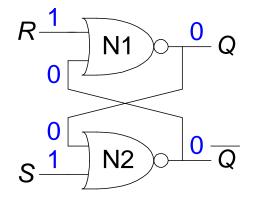

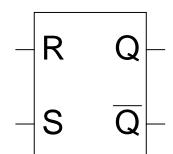

# SR Latch Symbol

- SR stands for Set/Reset Latch

- Stores one bit of state (Q)

- Control what value is being stored with *S*, *R* inputs

- Set: Make the output 1

$$(S=1, R=0, Q=1)$$

– Reset: Make the output 0

$$(S=0, R=1, Q=0)$$

Must do something to avoid

invalid state (when

$$S = R = 1$$

)

SR Latch Symbol

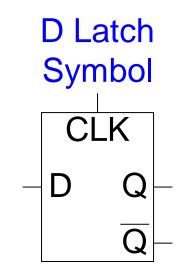

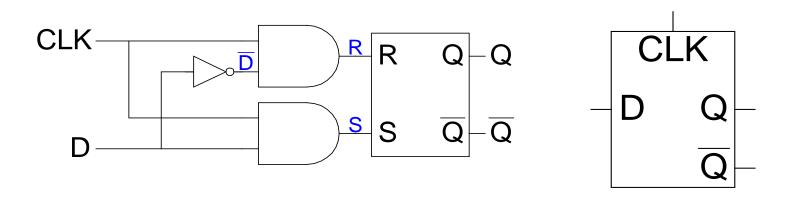

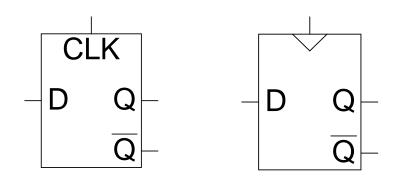

#### D Latch

- Two inputs: *CLK*, *D*

- *CLK*: controls *when* the output changes

- -D (the data input): controls what the output changes to

- Function

- When CLK = 1,

D passes through to Q(transparent)

- When *CLK* = 0,Q holds its previous value (*opaque*)

- Avoids invalid case when  $Q \neq \text{NOT } \overline{Q}$

#### D Latch Internal Circuit

| CLK | D | D | S | R | Q | Q |

|-----|---|---|---|---|---|---|

| 0   | X |   |   |   |   |   |

| 1   | 0 |   |   |   |   |   |

| 1   | 1 |   |   |   |   |   |

#### D Latch Internal Circuit

| CLK | D | D | S | R | Q         | Q                     |

|-----|---|---|---|---|-----------|-----------------------|

| 0   | X | X | 0 | 0 | $Q_{pre}$ | $\overline{Q}_{prev}$ |

| 1   | 0 | 1 | 0 | 1 | 0         | 1                     |

| 1   | 1 | 0 | 1 | 0 | 1         | 0                     |

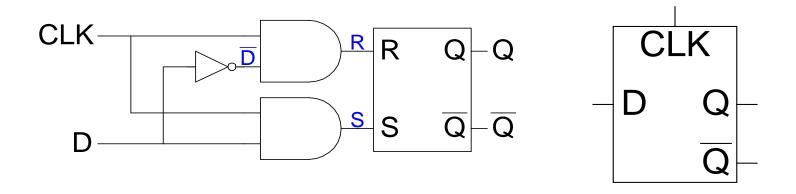

## D Flip-Flop

- Inputs: CLK, D

- Function

- Samples D on rising edge of CLK

- When *CLK* rises from 0 to 1, *D* passes through to *Q*

- Otherwise, Qholds its previous value

- Q changes only on rising edge of CLK

- Called *edge-triggered*

- Activated on the clock edge

D Flip-Flop Symbols

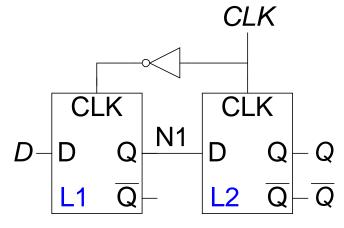

# D Flip-Flop Internal Circuit

- Two back-to-back latches (L1 and L2) controlled by complementary clocks

- When CLK = 0

- L1 is transparent

- L2 is opaque

- D passes through to N1

- When CLK = 1

- L2 is transparent

- L1 is opaque

- N1 passes through to Q

- Thus, on the edge of the clock (when CLK rises from  $0\rightarrow 1$ )

- D passes through to Q

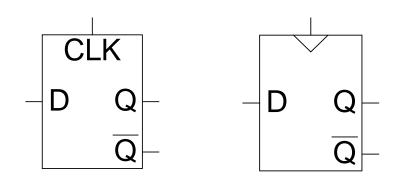

# D Latch vs. D Flip-Flop

CLK

D

Q (latch)

Q (flop)

# J D

# D Latch vs. D Flip-Flop

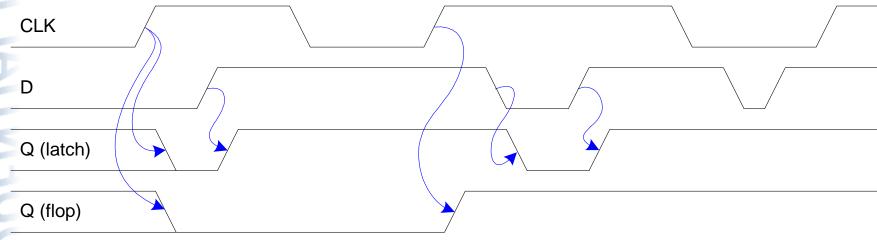

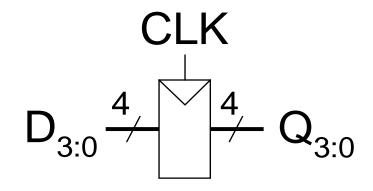

# Registers

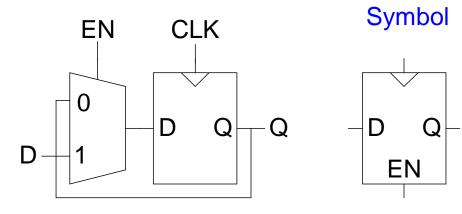

# **Enabled Flip-Flops**

- **Inputs:** *CLK*, *D*, *EN*

- The enable input (EN) controls when new data (D) is stored

- Function

- EN=1: D passes through to Q on the clock edge

- **EN**= **0**: the flip-flop retains its previous state

Internal Circuit

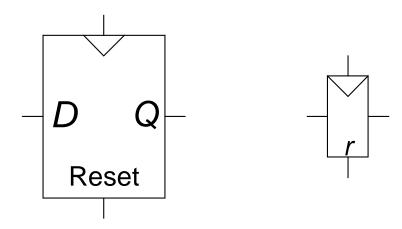

## Resettable Flip-Flops

- Inputs: CLK, D, Reset

- Function:

- **Reset** = 1: **Q** is forced to 0

- **Reset** = **0**: flip-flop behaves as ordinary D flip-flop

#### **Symbols**

#### Resettable Flip-Flops

- Two types:

- Synchronous: resets at the clock edge only

- **Asynchronous:** resets immediately when Reset = 1

- Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

- Synchronously resettable flip-flop?

## Resettable Flip-Flops

- Two types:

- Synchronous: resets at the clock edge only

- **Asynchronous:** resets immediately when Reset = 1

- Asynchronously resettable flip-flop requires changing the internal circuitry of the flip-flop

- Synchronously resettable flip-flop?

Internal

Circuit

CLK

D Q Q

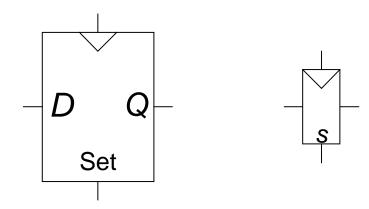

# Settable Flip-Flops

Inputs: CLK, D, Set

#### **Function:**

- **Set** = **1**: **Q** is set to 1

- **Set** = **0**: the flip-flop behaves as ordinary D flip-flop

#### **Symbols**

# Sequential Logic

- Sequential circuits: all circuits that aren't combinational

- A problematic circuit:

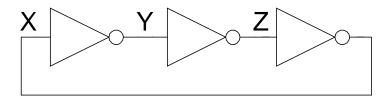

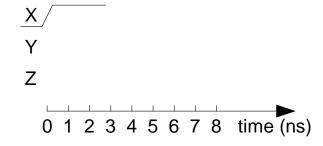

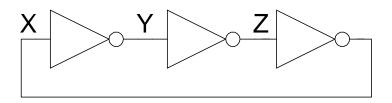

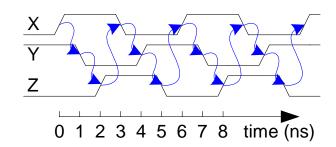

## Sequential Logic

- Sequential circuits: all circuits that aren't combinational

- A problematic circuit:

- No inputs and 1-3 outputs

- Astable circuit, oscillates

- Period depends on inverter delay

- It has a *cyclic path*: output fed back to input

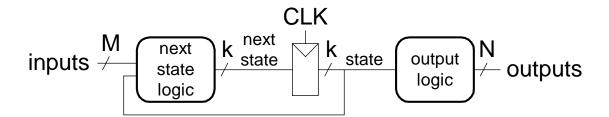

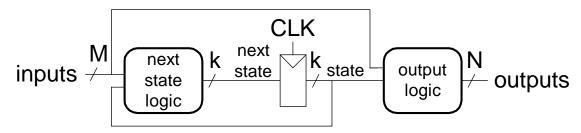

#### Synchronous Sequential Logic Design

- Breaks cyclic paths by inserting registers

- Registers contain **state** of the system

- State changes at clock edge: system **synchronized** to the clock

- Rules of synchronous sequential circuit composition:

- Every circuit element is either a register or a combinational circuit

- At least one circuit element is a register

- All registers receive the same clock signal

- Every cyclic path contains at least one register

- Two common synchronous sequential circuits

- Finite State Machines (FSMs)

- Pipelines

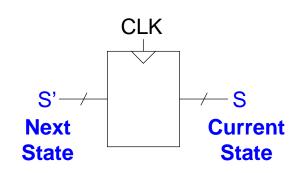

# Finite State Machine (FSM)

- Consists of:

- -State register

- Stores current state

- Loads next state at clock edge

- Computes the next state

- Computes the outputs

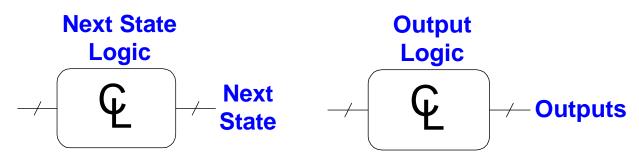

## Finite State Machines (FSMs)

- Next state determined by current state and inputs

- Two types of finite state machines differ in output logic:

- Moore FSM: outputs depend only on current state

- Mealy FSM: outputs depend on current state and inputs

#### Moore FSM

#### Mealy FSM

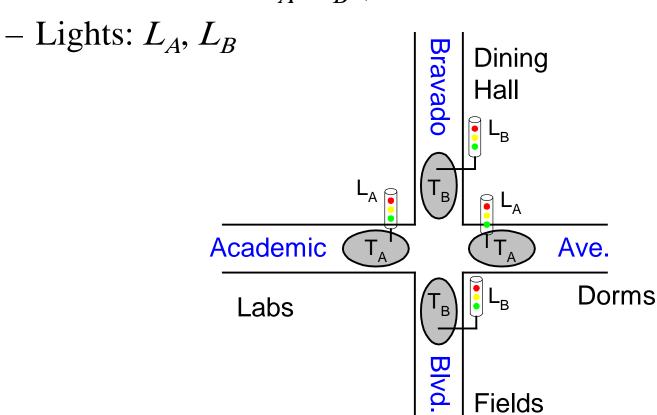

# FSM Example

Traffic light controller

- Traffic sensors:  $T_A$ ,  $T_B$  (TRUE when there's traffic)

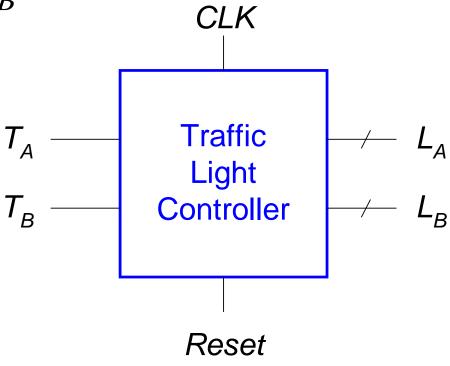

### FSM Black Box

- Inputs: CLK, Reset,  $T_A$ ,  $T_B$

- Outputs:  $L_A$ ,  $L_B$

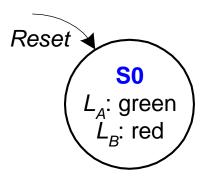

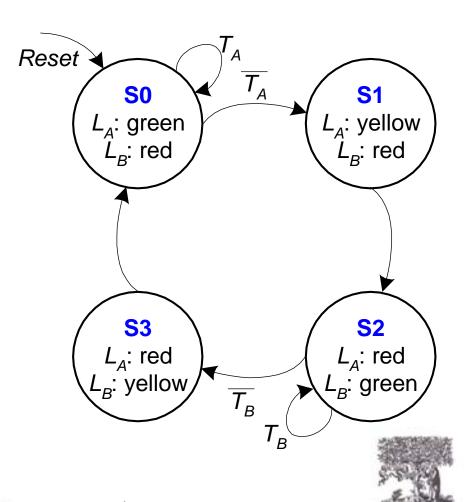

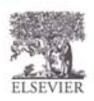

### FSM State Transition Diagram

- Moore FSM: outputs labeled in each state

- **States:** Circles

- Transitions: Arcs

### **FSM State Transition Diagram**

- Moore FSM: outputs labeled in each state

- States: Circles

- Transitions: Arcs

### **FSM State Transition Table**

| Current<br>State | Inputs    |         | Next<br>State |

|------------------|-----------|---------|---------------|

| S                | $T_{\!A}$ | $T_{B}$ | S'            |

| <b>S</b> 0       | 0         | X       |               |

| <b>S</b> 0       | 1         | X       |               |

| <b>S</b> 1       | X         | X       |               |

| S2               | X         | 0       |               |

| S2               | X         | 1       |               |

| <b>S</b> 3       | X         | X       |               |

### **FSM State Transition Table**

| Current<br>State           | Inputs    |         | Next<br>State |

|----------------------------|-----------|---------|---------------|

| $\boldsymbol{\mathcal{S}}$ | $T_{\!A}$ | $T_{B}$ | S'            |

| S0                         | 0         | X       | <b>S</b> 1    |

| S0                         | 1         | X       | S0            |

| <b>S</b> 1                 | X         | X       | S2            |

| S2                         | X         | 0       | S3            |

| S2                         | X         | 1       | S2            |

| <b>S</b> 3                 | X         | X       | S0            |

# UENTIAL LOGIC

### FSM Encoded State Transition Table

| Curren | t State | Inp       | uts     | Next   | State  |

|--------|---------|-----------|---------|--------|--------|

| $S_1$  | $S_0$   | $T_{\!A}$ | $T_{B}$ | $S_1'$ | $S_0'$ |

| 0      | 0       | 0         | X       |        |        |

| 0      | 0       | 1         | X       |        |        |

| 0      | 1       | X         | X       |        |        |

| 1      | 0       | X         | 0       |        |        |

| 1      | 0       | X         | 1       |        |        |

| 1      | 1       | X         | X       |        |        |

| State      | Encoding |

|------------|----------|

| <b>S</b> 0 | 00       |

| <b>S</b> 1 | 01       |

| S2         | 10       |

| S3         | 11       |

# UENTIAL LOGIC

### FSM Encoded State Transition Table

| Curren | t State | Inp     | uts     | Next   | State  |

|--------|---------|---------|---------|--------|--------|

| $S_1$  | $S_0$   | $T_{A}$ | $T_{B}$ | $S_1'$ | $S_0'$ |

| 0      | 0       | 0       | X       | 0      | 1      |

| 0      | 0       | 1       | X       | 0      | 0      |

| 0      | 1       | X       | X       | 1      | 0      |

| 1      | 0       | X       | 0       | 1      | 1      |

| 1      | 0       | X       | 1       | 1      | 0      |

| 1      | 1       | X       | X       | 0      | 0      |

| State      | Encoding |

|------------|----------|

| S0         | 00       |

| <b>S</b> 1 | 01       |

| S2         | 10       |

| S3         | 11       |

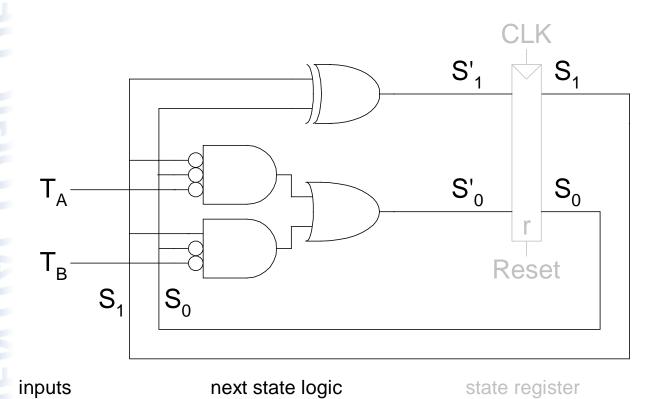

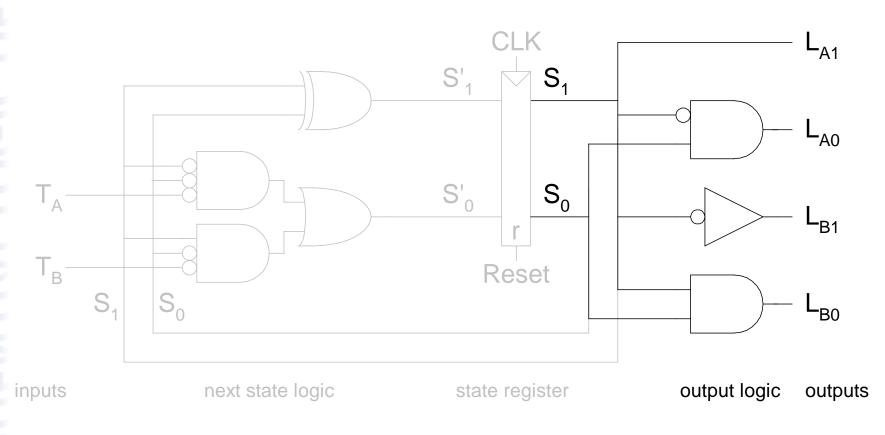

$$S_1' = S_1 \oplus S_0$$

$$S_0' = \overline{S_1} \overline{S_0} \overline{T_A} + S_1 \overline{S_0} \overline{T_B}$$

## FSM Output Table

| Curren | t State | Outputs  |          | outs     |          |

|--------|---------|----------|----------|----------|----------|

| $S_1$  | $S_0$   | $L_{A1}$ | $L_{A0}$ | $L_{B1}$ | $L_{B0}$ |

| 0      | 0       |          |          |          |          |

| 0      | 1       |          |          |          |          |

| 1      | 0       |          |          |          |          |

| 1      | 1       |          |          |          |          |

| Output | Encoding |

|--------|----------|

| green  | 00       |

| yellow | 01       |

| red    | 10       |

### FSM Output Table

| Curren | t State | Outputs  |          |          |          |

|--------|---------|----------|----------|----------|----------|

| $S_1$  | $S_0$   | $L_{A1}$ | $L_{A0}$ | $L_{B1}$ | $L_{B0}$ |

| 0      | 0       | 0        | 0        | 1        | 0        |

| 0      | 1       | 0        | 1        | 1        | 0        |

| 1      | 0       | 1        | 0        | 0        | 0        |

| 1      | 1       | 1        | 0        | 0        | 1        |

| Output | Encoding |

|--------|----------|

| green  | 00       |

| yellow | 01       |

| red    | 10       |

$$L_{A1} = S_1$$

$$L_{A0} = \overline{S_1}S_0$$

$$L_{B1} = \overline{S_1}$$

$$L_{B0} = S_1S_0$$

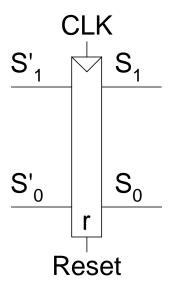

# FSM Schematic: State Register

state register

### FSM Schematic: Next State Logic

# FSM Schematic: Output Logic

# FSM Timing Diagram

# FSM State Encoding

- Binary encoding:

- i.e., for four states, 00, 01, 10, 11

- One-hot encoding

- One state bit per state

- Only one state bit HIGH at once

- i.e., for 4 states, 0001, 0010, 0100, 1000

- Requires more flip-flops

- Often next state and output logic is simpler

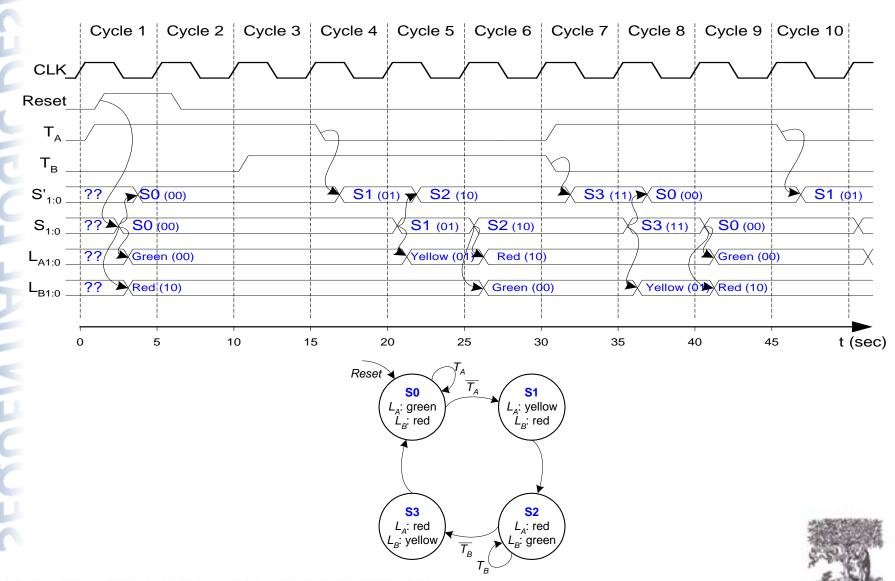

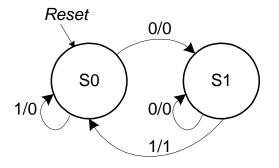

### Moore vs. Mealy FSM

Alyssa P. Hacker has a snail that crawls down a paper tape with 1's and 0's on it. The snail smiles whenever the last two digits it has crawled over are 01. Design Moore and Mealy FSMs of the snail's brain.

### State Transition Diagrams

### **Moore FSM**

### **Mealy FSM**

Mealy FSM: arcs indicate input/output

### Moore FSM State Transition Table

| Current<br>State |       | Inputs | Next   | State  |

|------------------|-------|--------|--------|--------|

| $S_1$            | $S_0$ | A      | $S_1'$ | $S_0'$ |

| 0                | 0     | 0      |        |        |

| 0                | 0     | 1      |        |        |

| 0                | 1     | 0      |        |        |

| 0                | 1     | 1      |        |        |

| 1                | 0     | 0      |        |        |

| 1                | 0     | 1      |        |        |

| State | Encoding |

|-------|----------|

| S0    | 00       |

| S1    | 01       |

| S2    | 10       |

### Moore FSM State Transition Table

| Current<br>State |       | Inputs | Next   | State  |

|------------------|-------|--------|--------|--------|

| $S_1$            | $S_0$ | A      | $S_1'$ | $S_0'$ |

| 0                | 0     | 0      | 0      | 1      |

| 0                | 0     | 1      | 0      | 0      |

| 0                | 1     | 0      | 0      | 1      |

| 0                | 1     | 1      | 1      | 0      |

| 1                | 0     | 0      | 0      | 1      |

| 1                | 0     | 1      | 0      | 0      |

| State      | Encoding |

|------------|----------|

| S0         | 00       |

| <b>S</b> 1 | 01       |

| <b>S</b> 2 | 10       |

$$S_1' = S_0 A$$

$S_0' = \overline{A}$

# Moore FSM Output Table

| Current State |         | Output |

|---------------|---------|--------|

| $S_1$         | $S_{0}$ | Y      |

| 0             | 0       |        |

| 0             | 1       |        |

| 1             | 0       |        |

# Moore FSM Output Table

| Current State |       | Output |

|---------------|-------|--------|

| $S_1$         | $S_0$ | Y      |

| 0             | 0     | 0      |

| 0             | 1     | 0      |

| 1             | 0     | 1      |

$$Y=S_1$$

### Mealy FSM State Transition & Output Table

| Current<br>State | Input | Next<br>State | Output |

|------------------|-------|---------------|--------|

| $S_0$            | A     | ${\cal S}_0'$ | Y      |

| 0                | 0     |               |        |

| 0                | 1     |               |        |

| 1                | 0     |               |        |

| 1                | 1     |               |        |

| State      | Encoding |

|------------|----------|

| <b>S</b> 0 | 00       |

| <b>S</b> 1 | 01       |

### Mealy FSM State Transition & Output Table

| Current<br>State | Input | Next<br>State | Output |

|------------------|-------|---------------|--------|

| $S_0$            | A     | ${\cal S}_0'$ | Y      |

| 0                | 0     | 1             | 0      |

| 0                | 1     | 0             | 0      |

| 1                | 0     | 1             | 0      |

| 1                | 1     | 0             | 1      |

| State      | Encoding |

|------------|----------|

| S0         | 00       |

| <b>S</b> 1 | 01       |

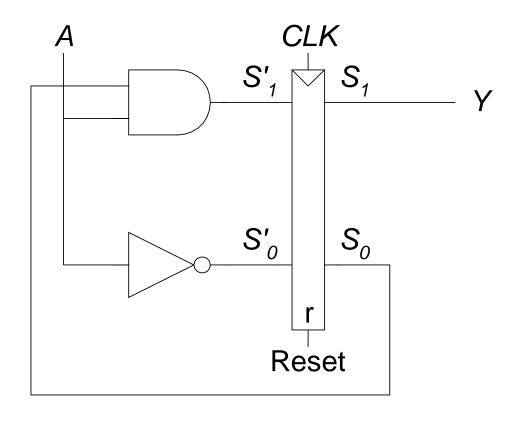

### Moore FSM Schematic

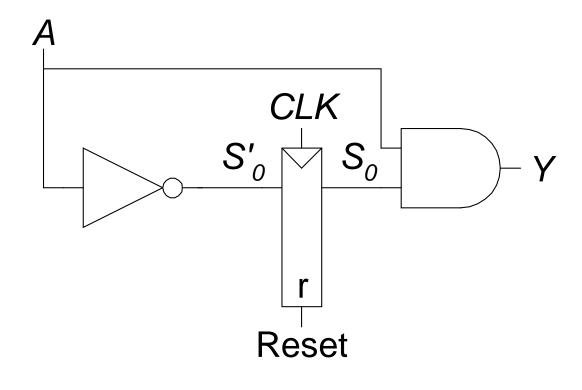

# Mealy FSM Schematic

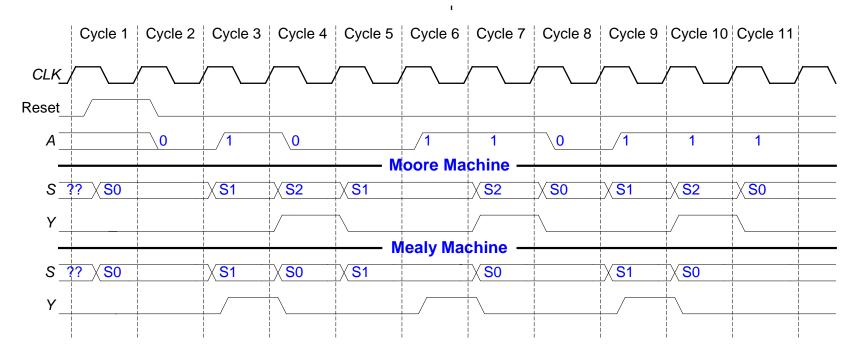

# Moore & Mealy Timing Diagram

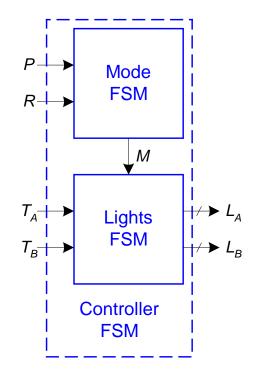

### Factoring State Machines

- Break complex FSMs into smaller interacting FSMs

- Example: Modify traffic light controller to have Parade Mode.

- Two more inputs: P, R

- When P = 1, enter Parade Mode & Bravado Blvd light stays green

- When R = 1, leave Parade Mode

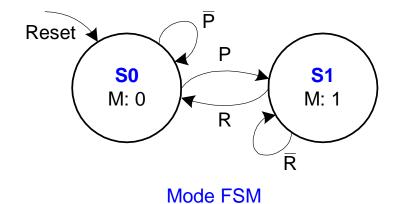

### Parade FSM

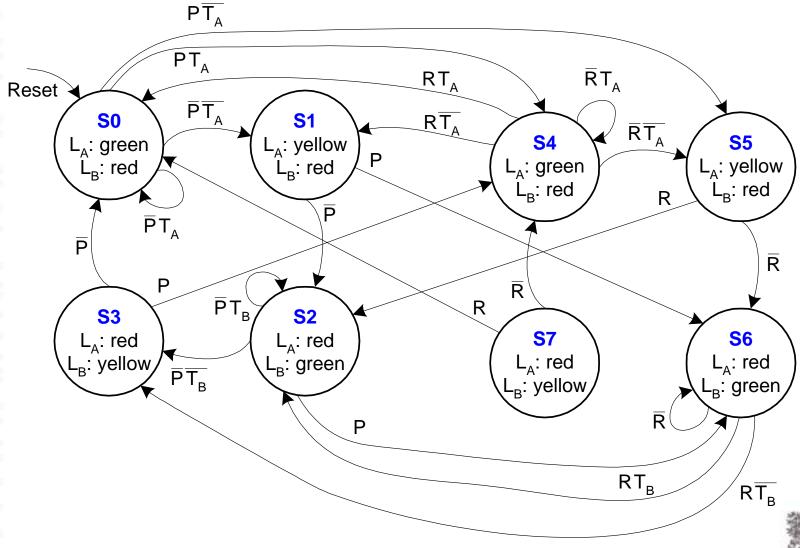

### **Unfactored FSM**

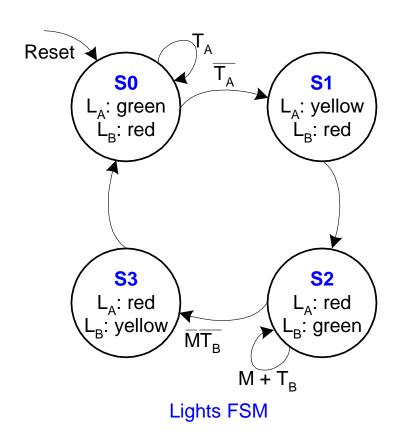

### **Factored FSM**

### Unfactored FSM

### Factored FSM

ELSEVIER

### FSM Design Procedure

- Identify inputs and outputs

- Sketch state transition diagram

- Write state transition table

- Select state encodings

- For Moore machine:

- Rewrite state transition table with state encodings

- Write output table

- **6**. For a Mealy machine:

- Rewrite combined state transition and output table with state encodings

- Write Boolean equations for next state and output logic

- Sketch the circuit schematic

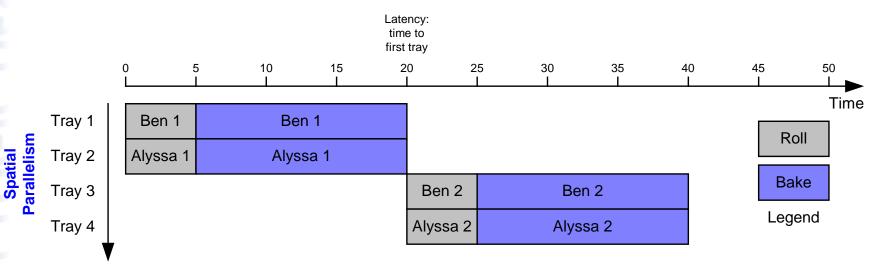

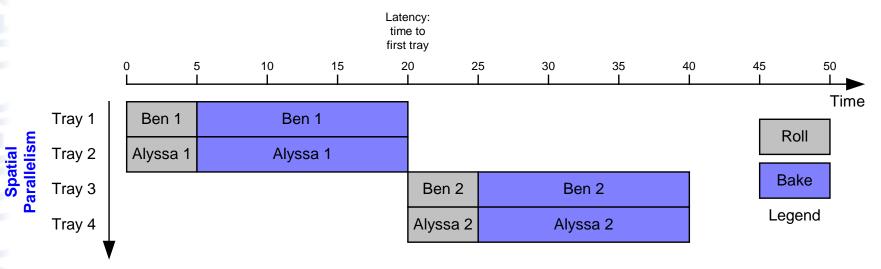

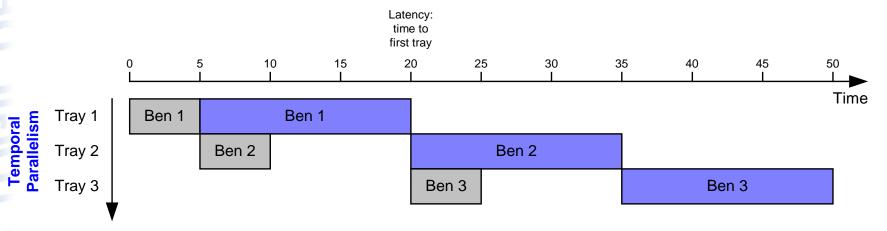

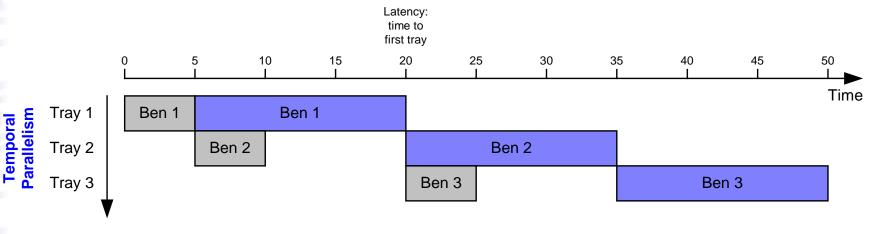

### Parallelism

### Two types of parallelism:

- Spatial parallelism

- duplicate hardware performs multiple tasks at once

- Temporal parallelism

- task is broken into multiple stages

- also called pipelining

- for example, an assembly line

### Parallelism Definitions

- Token: Group of inputs processed to produce group of outputs

- Latency: Time for one token to pass from start to end

- Throughput: Number of tokens produced per unit time

Parallelism increases throughput

## Parallelism Example

- Ben Bitdiddle bakes cookies to celebrate traffic light controller installation

- 5 minutes to roll cookies

- 15 minutes to bake

- What is the latency and throughput without parallelism?

### Parallelism Example

- Ben Bitdiddle bakes cookies to celebrate traffic light controller installation

- 5 minutes to roll cookies

- 15 minutes to bake

- What is the latency and throughput without parallelism?

Latency = 5 + 15 = 20 minutes = 1/3 hour

**Throughput** = 1 tray / 1/3 hour = 3 trays/hour

### Parallelism Example

- What is the latency and throughput if Ben uses parallelism?

- Spatial parallelism: Ben asks Allysa P. Hacker to help, using her own oven

- Temporal parallelism:

- two stages: rolling and baking

- He uses two trays

- While first batch is baking, he rolls the second batch, etc.

# Spatial Parallelism

Latency = ?

Throughput = ?

# Spatial Parallelism

Latency =

$$5 + 15 = 20$$

minutes =  $1/3$  hour

**Throughput** = 2 trays/ 1/3 hour = 6 trays/hour

# Temporal Parallelism

Latency = ?

**Throughput** = ?

# UENTIA

### Temporal Parallelism

Latency =

$$5 + 15 = 20$$

minutes =  $1/3$  hour

**Throughput** = 1 trays/ 1/4 hour = 4 trays/hour

Using both techniques, the throughput would be 8 trays/hour